Verilog

31条指令单周期cpu设计(Verilog)-(六)指令操作时间表设计

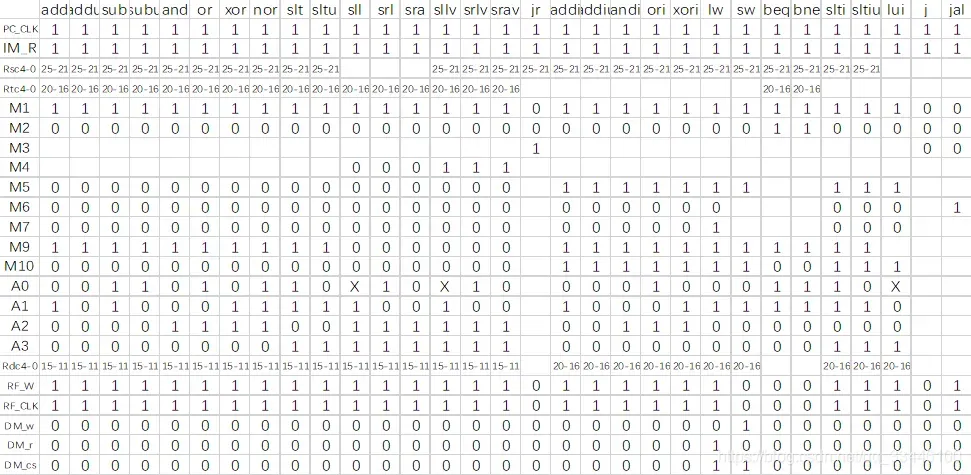

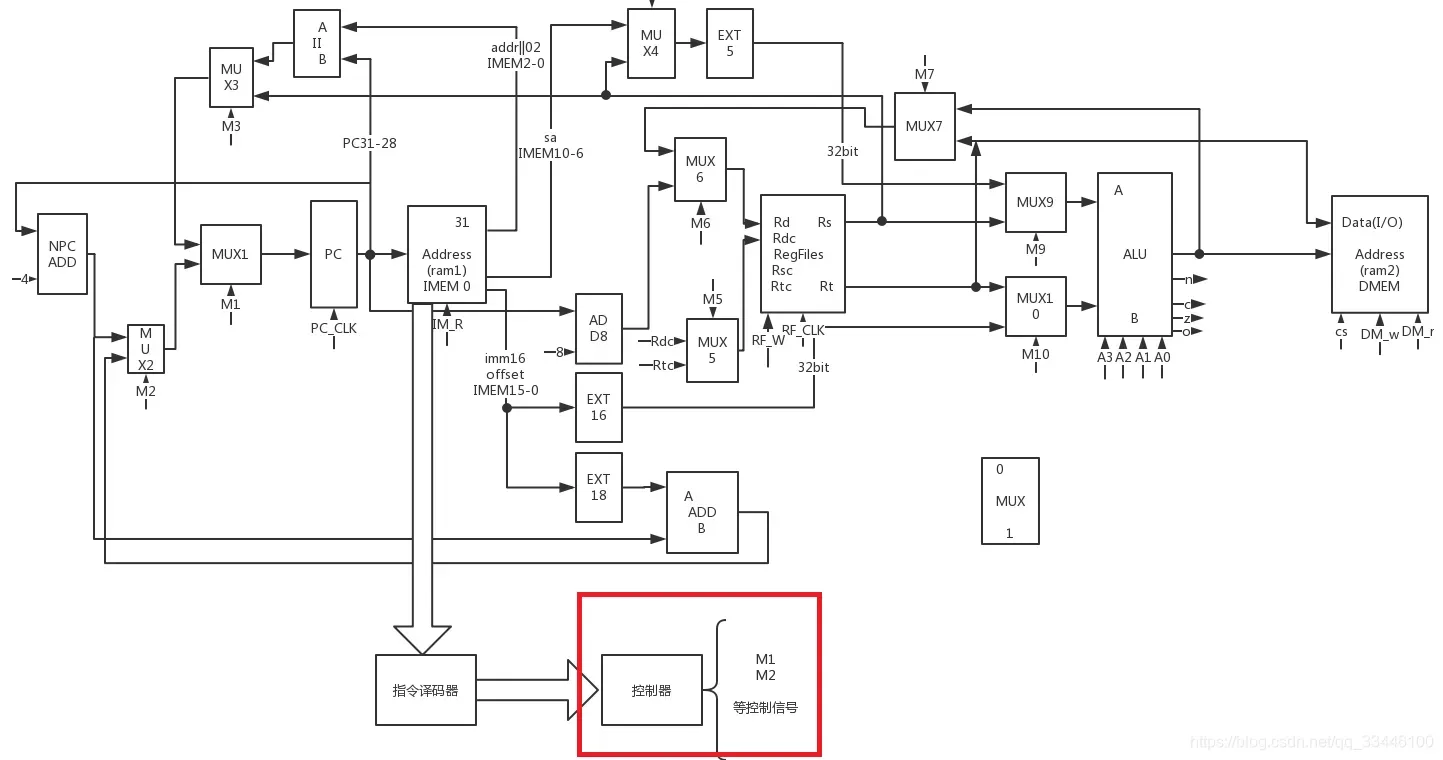

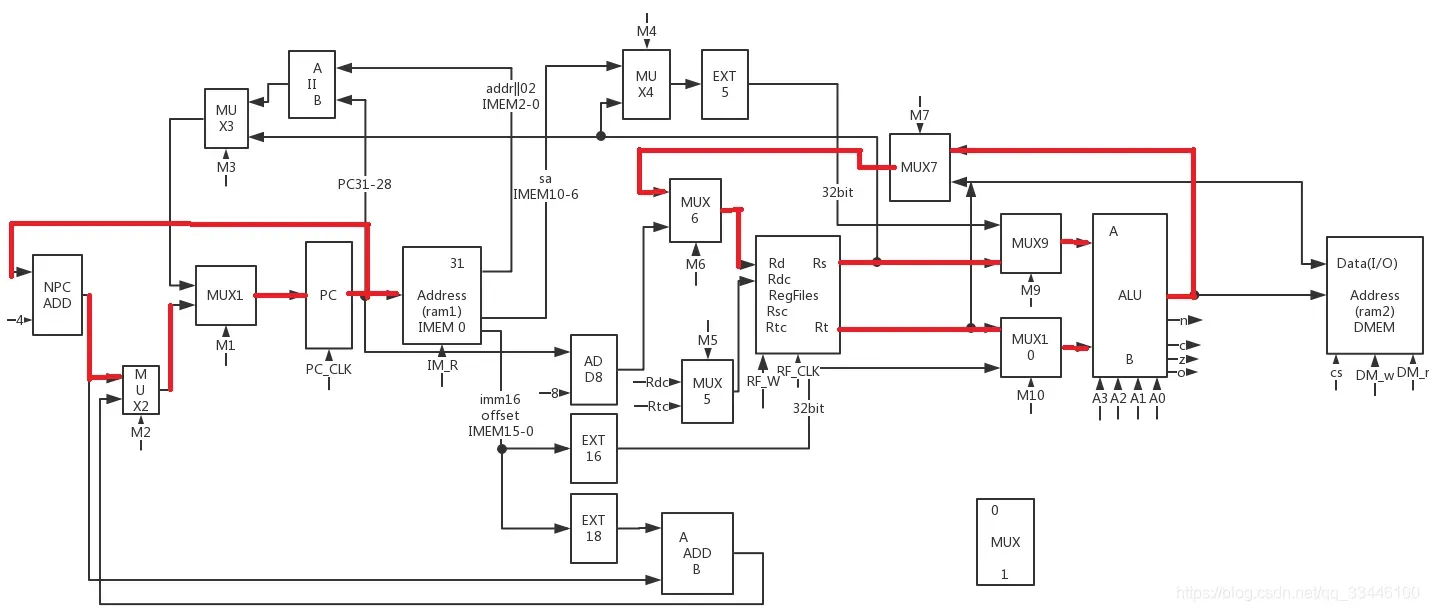

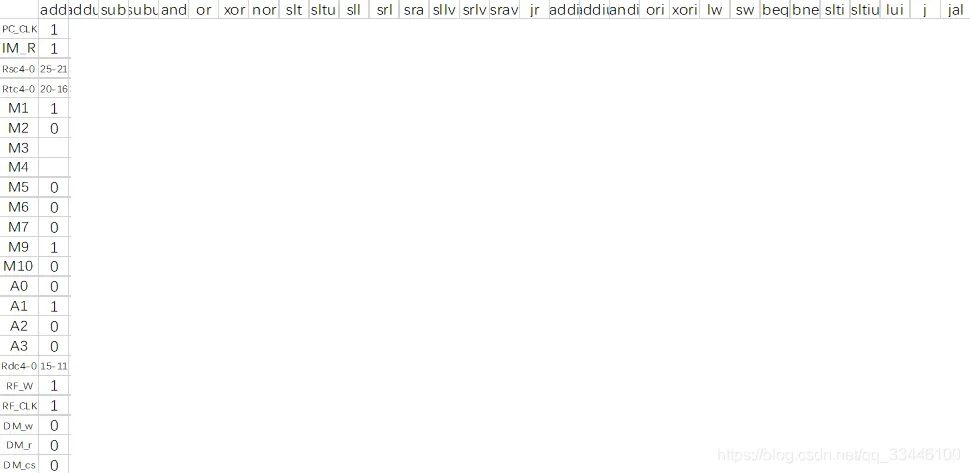

详解31条MIPS单周期CPU的指令操作时间表设计,包括控制器真值表设计方法、各控制信号的作用说明,以及基于数据通路图的控制器实现步骤。

说在前面

- 开发环境:Vivado

- 语言:Verilog

- cpu框架:Mips

- 控制器:组合逻辑

设计目的

- 这张表格又是干啥的呢(+_+)?

- 废话少说,用来设计控制器的 (红色方框)

设计流程

- 表头为31条指令,首列为所有的控制信号

(控制信号需要解释吗?) 控制信号取值为0/1,上面表格中的Rsc、Rtc、Rdc是寄存器的输入

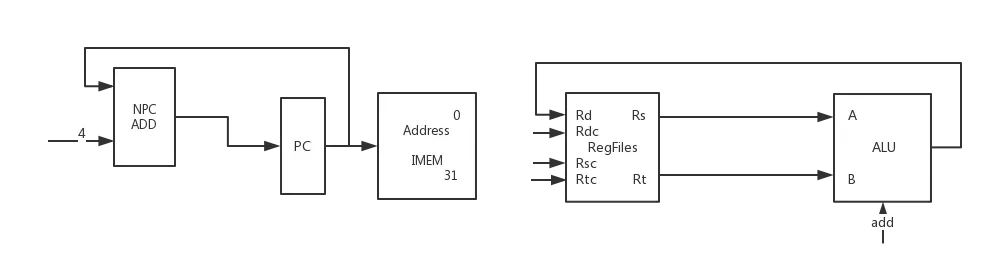

控制信号取值为0/1,上面表格中的Rsc、Rtc、Rdc是寄存器的输入 (应该设计过寄存器吧?)M开头 MUX控制信号 A开头 ALU控制信号 RF_W 寄存器堆写入enable信号 PC_CLK pc寄存器enable信号 IM_R 指令存储器控制信号 DM开头 数据存储器控制信号 - 根据每一条指令的数据通路图确定控制信号的值;以add为例

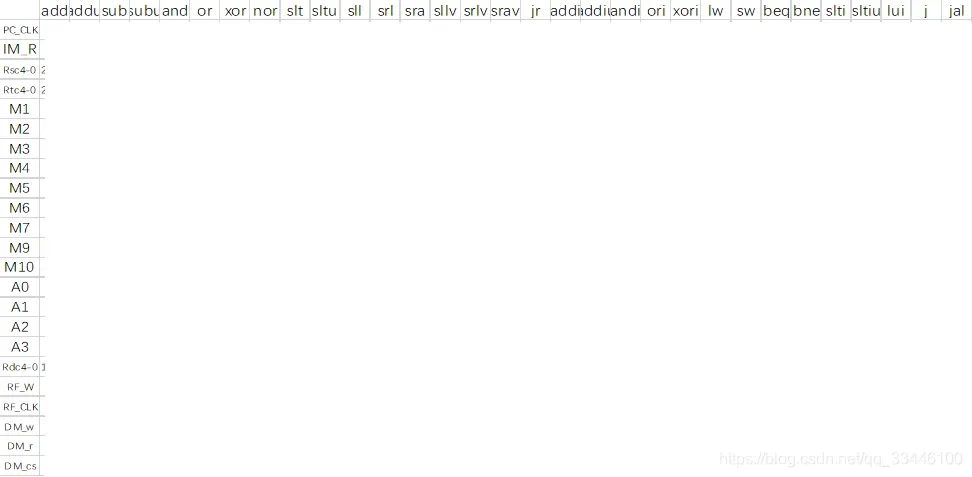

对比可以完善表格为(未涉及的控制信号可以不填):

对比可以完善表格为(未涉及的控制信号可以不填):

- 重复以上步骤,设计其他指令的控制器