Verilog

31条指令单周期cpu设计(Verilog)-(三)指令分析

详细分析31条MIPS指令的数据通路设计,包括ADD、SUB、LW、SW、JAL等指令的部件需求、输入输出关系和数据通路图,附完整Verilog实现参考。

说在前面

- 开发环境:Vivado

- 语言:Verilog

- cpu框架:Mips

- 控制器:组合逻辑

- 鸽鸽鸽。。。

指令分析流程

- 确定一条指令所需要的具体操作

- 分析该条指令中涉及的部件

- 确定各个部件的输入输出关系

- 画出数据通路图

例子

- 以ADD为例

- 首先我们需要根据PC从指令集合中取出这条指令,然后将两个操作数相加 Rrd→Rrs+Rrt ,最后将PC+4,指向下一条指令;

- 涉及部件:PC寄存器、指令存储器、寄存器、ALU

- 输入输出关系

指令 PC IM RF ALU WData A B ADD PC+4 PC ALU RF.RD1 RF.RD2 - 数据通路图

31条指令分析

字符说明

| NPC | IMEM | RegFiles | IR | DMEM |

|---|---|---|---|---|

| 即PC+4,可以使用简单的加法实现 | 指令存储器 | 寄存器堆 | 指令寄存器 | 数据存储器 |

| PC | ADD8 | EXTn | MUX | |

| 指令计数器 | 加8操作 | 将n位扩展 | 多路选择器 |

先放总结

- 在分析指令的时候一定要参考详细的指令说明,在上一篇中有,这样可以帮助理解指令过程;

- 这31条指令看似很多

(其实真的很多),但是里面还是有很多是相似的,所以数据通路图几乎一样; - 比较难的几条指令:lw、sw、jal、beq

- 建议自己分析一遍

(很重要) - 下一篇将分析两张很大很大的表格,指令操作时间表以及整体数据输入输出关系表,这两张表对于整体的数据通路的设计以及控制器设计十分重要!!!

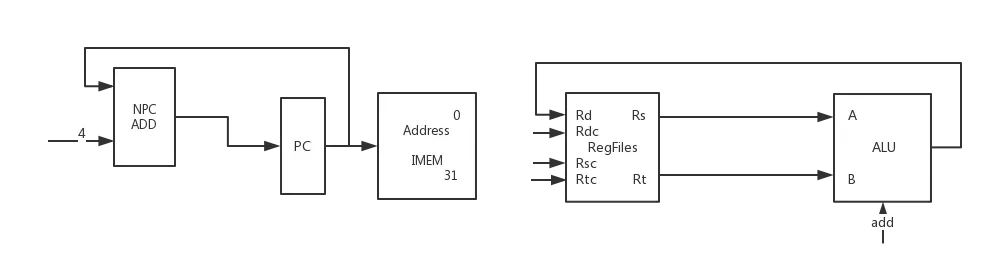

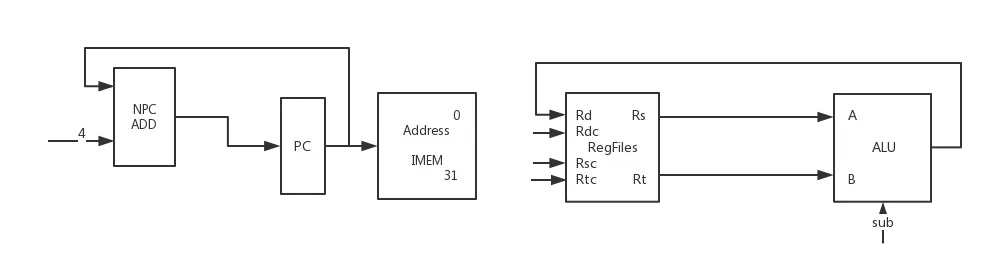

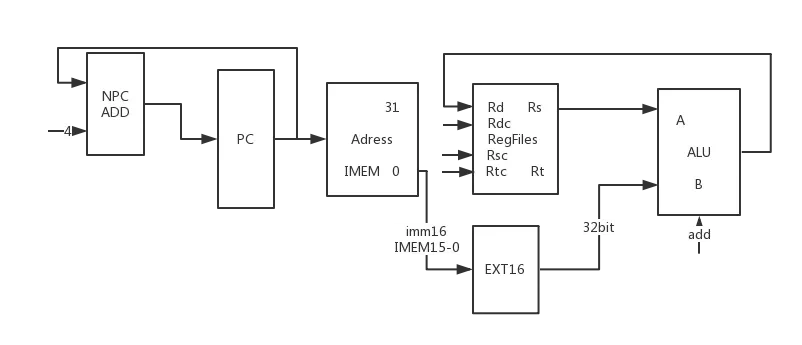

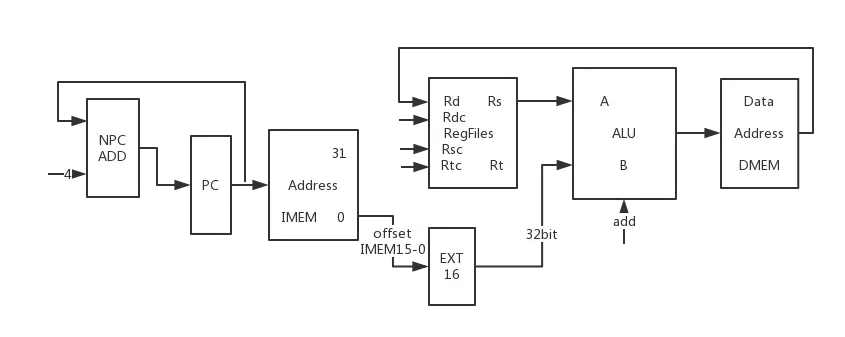

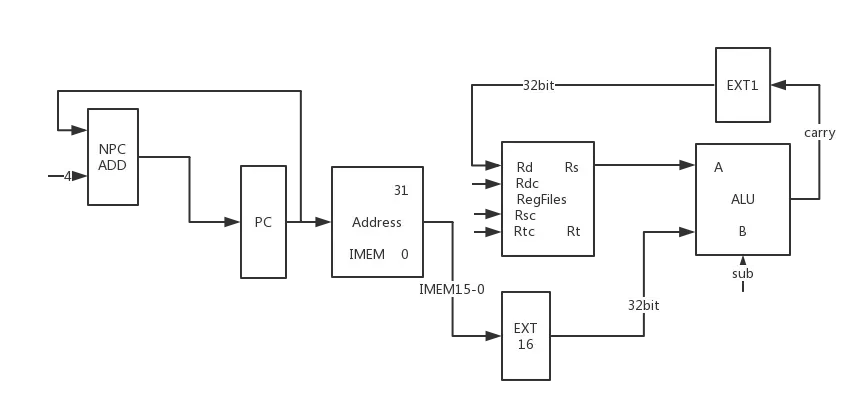

add

- 格式:add rd, rs, rt

- 描述:rd ← rs + rt; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU

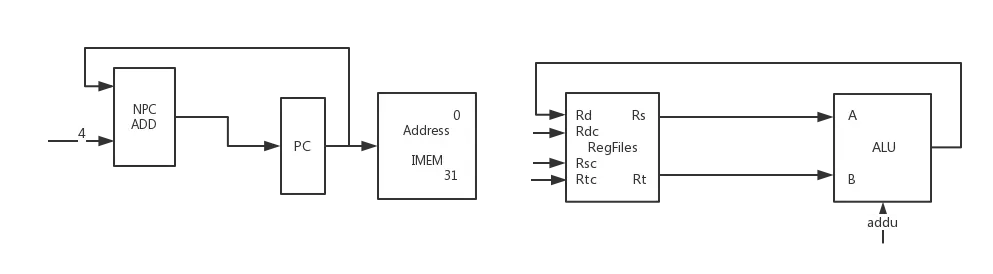

addu

- 格式:addu rd, rs, rt

- 描述:rd ← rs + rt; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU

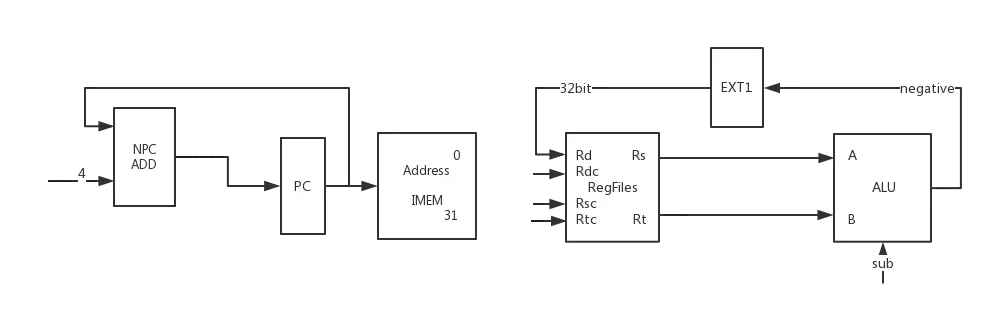

sub

- 格式:sub rd, rs, rt

- 描述:rd ← rs - rt; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU

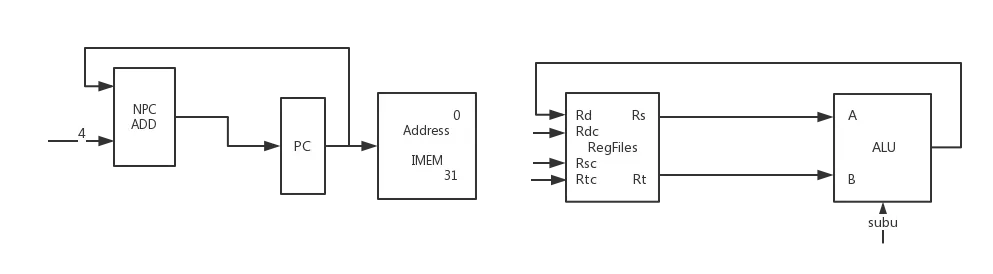

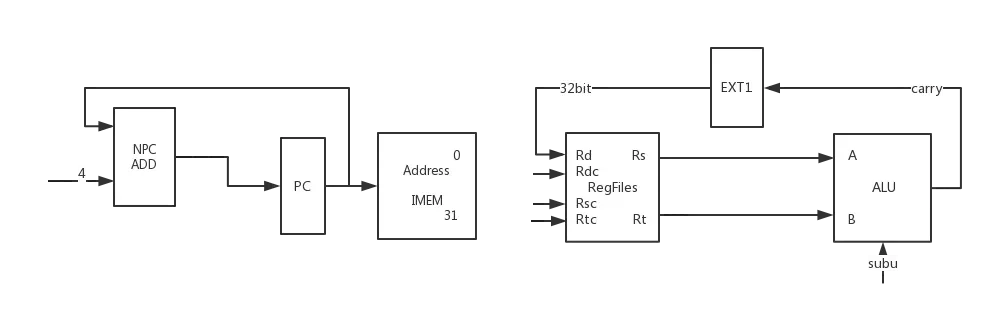

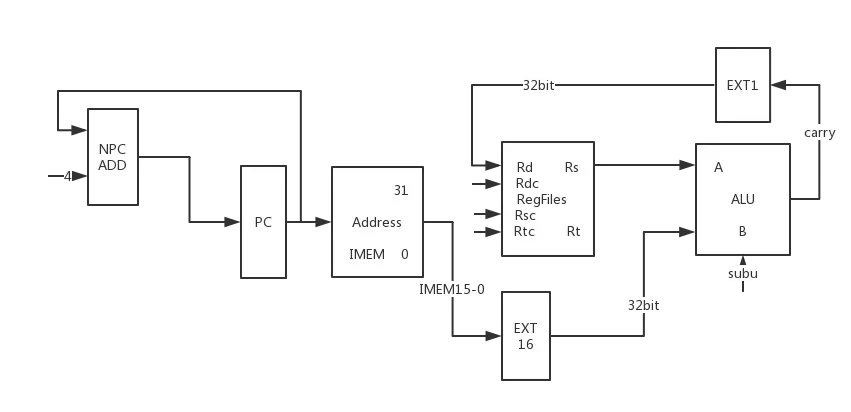

subu

- 格式:subu rd, rs, rt

- 描述:rd ← rs - rt; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU

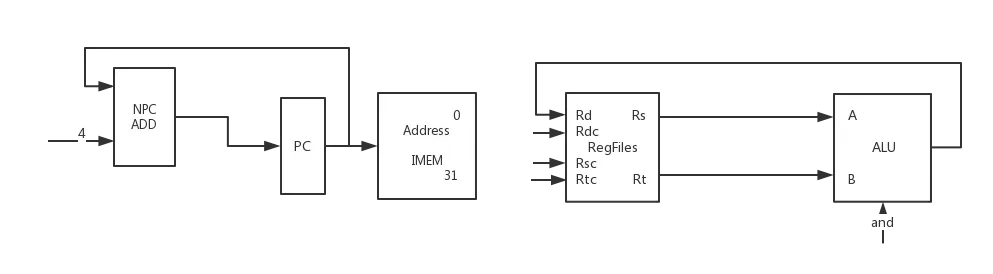

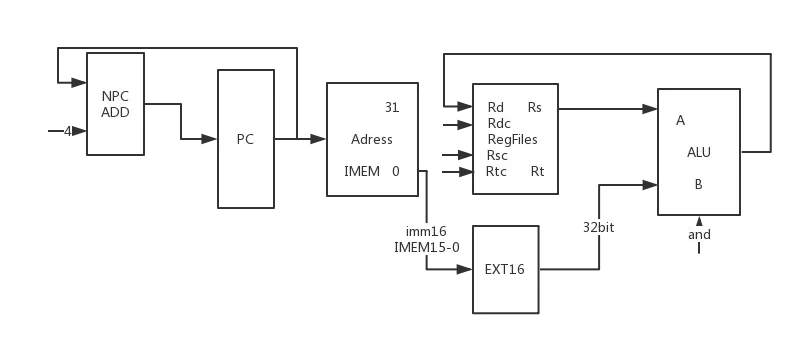

and

- 格式:and rd, rs, rt

- 描述:rd ← rs and rt; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU

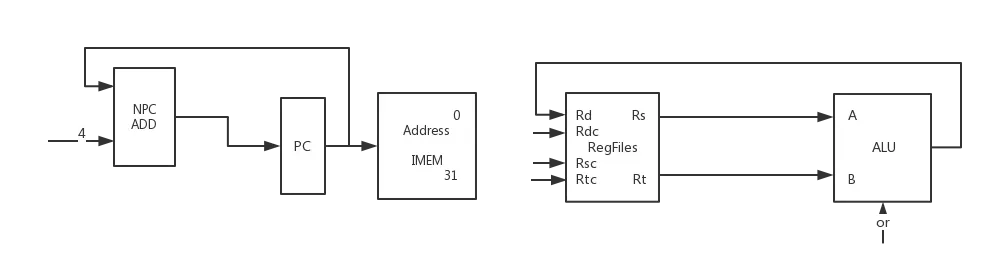

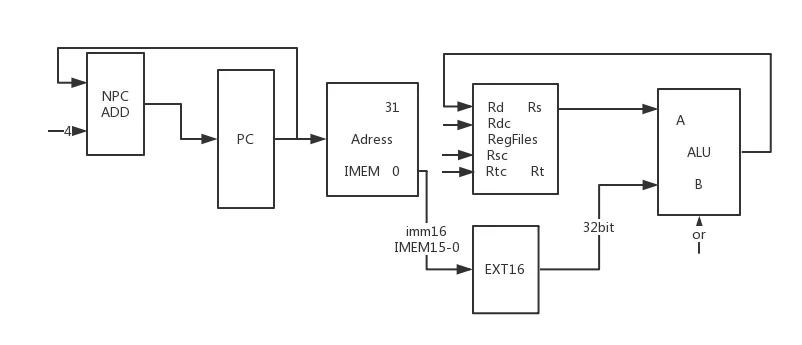

or

- 格式:or rd, rs, rt

- 描述:rd ← rs or rt; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU

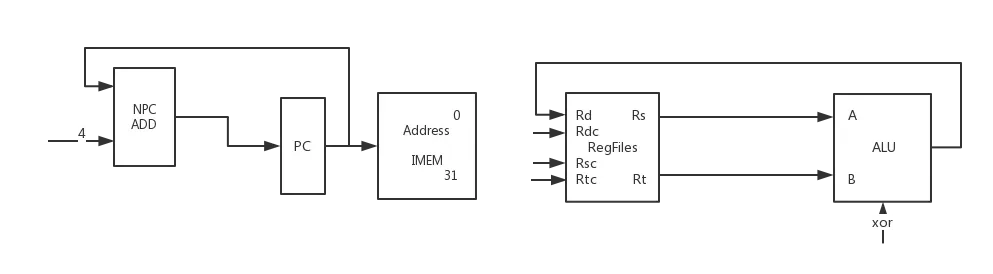

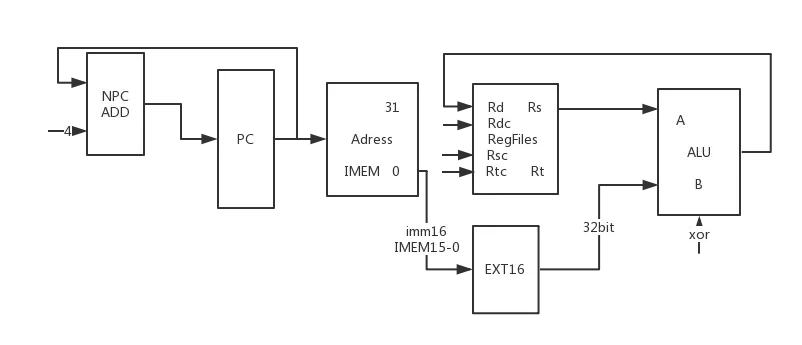

xor

- 格式:xor rd, rs, rt

- 描述:rd ← rs xor rt; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU

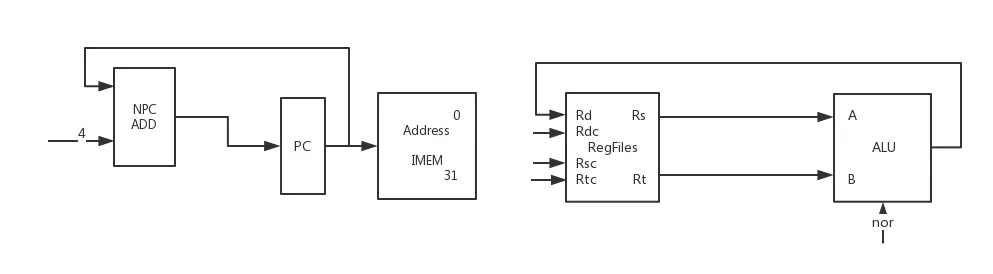

nor

- 格式:nor rd, rs, rt

- 描述:rd ← rs nor rt; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU

slt

- 格式:slt rd, rs, rt

- 描述:rd ← (rs < rt); PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT1

sltu

- 格式:sltu rd, rs, rt

- 描述:rd ← (rs < rt); PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT1

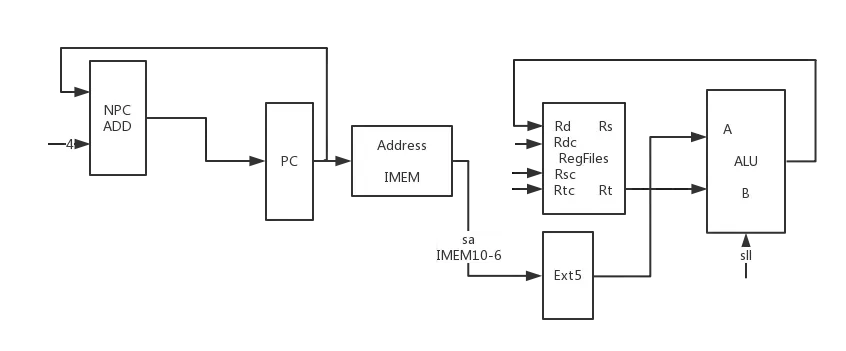

sll

- 格式:sll rd, rt, sa

- 描述:rd ← rt << sa (logical); PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、Ext5

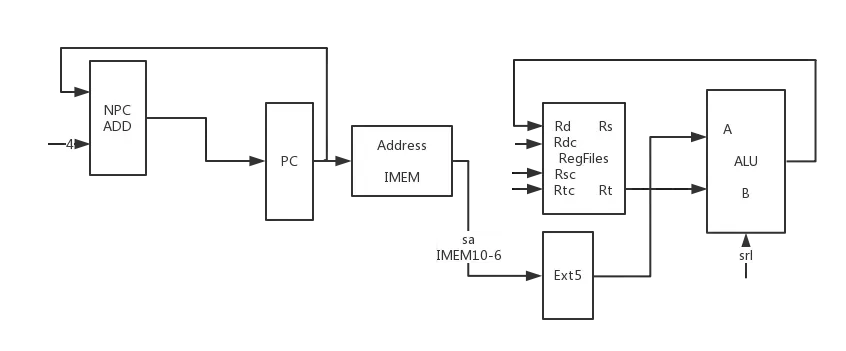

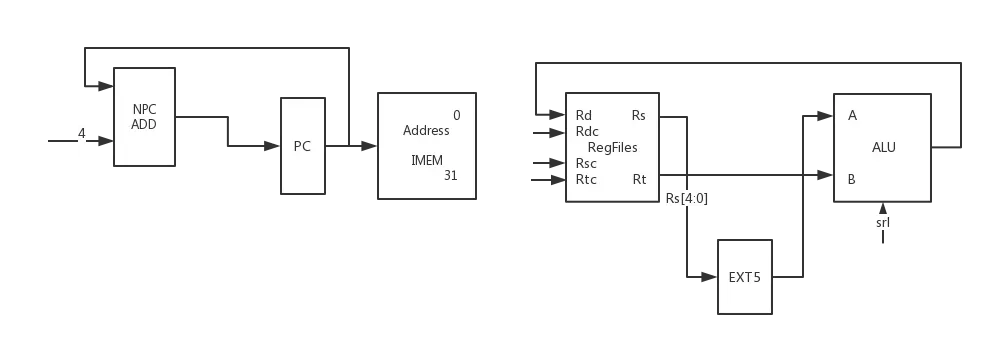

srl

- 格式:srl rd, rt, sa

- 描述: rd ← rt >> sa (logical); PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、Ext5

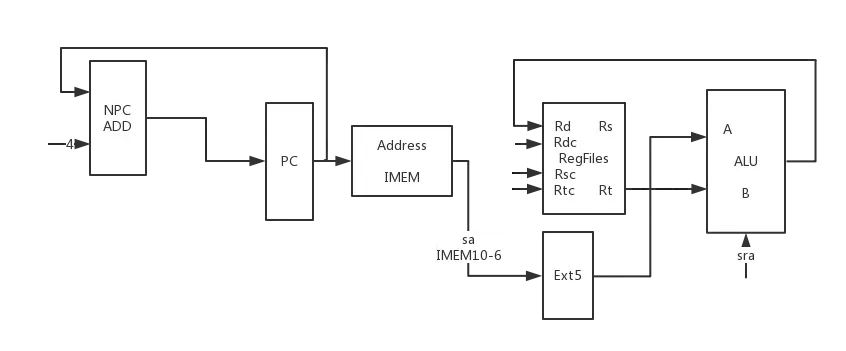

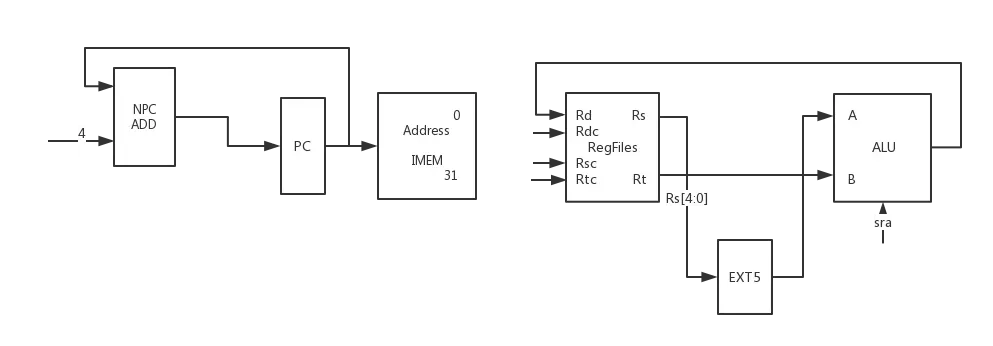

sra

- 格式:sra rd, rt, sa

- 描述: rd ← rt >> sa (arithmetic); PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、Ext5

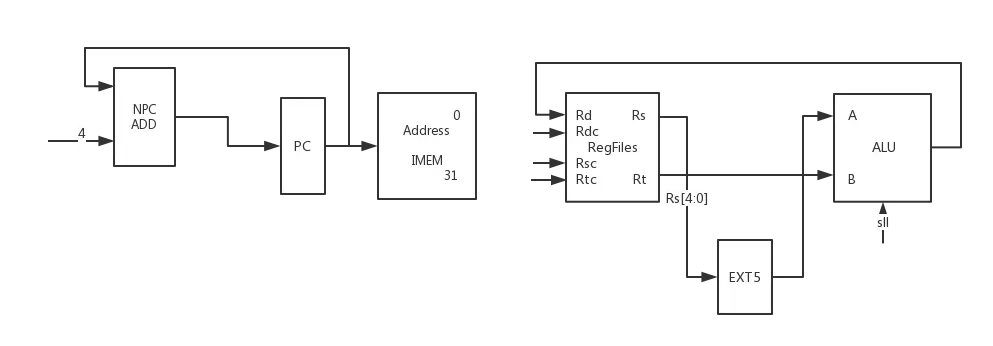

sllv

- 格式:sllv rd, rt, rs

- 描述:rd ← rt << rs 4:0 (logical); PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT5

srlv

- 格式:srlv rd, rt, rs

- 描述:rd ← rt >> rs 4:0 (logical); PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT5

srav

- 格式:srav rd, rt, rs

- 描述:rd ← rt >> rs 4:0 (arithmetic); PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT5

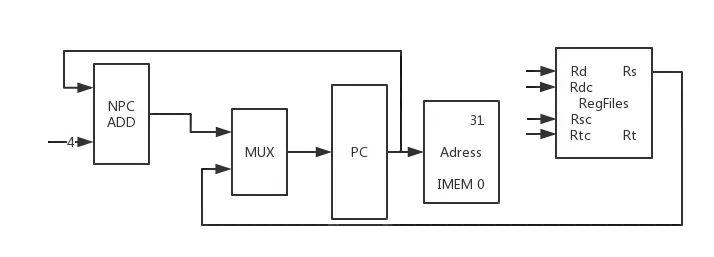

jr

- 格式:jr rs

- 描述:PC ← rs; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles

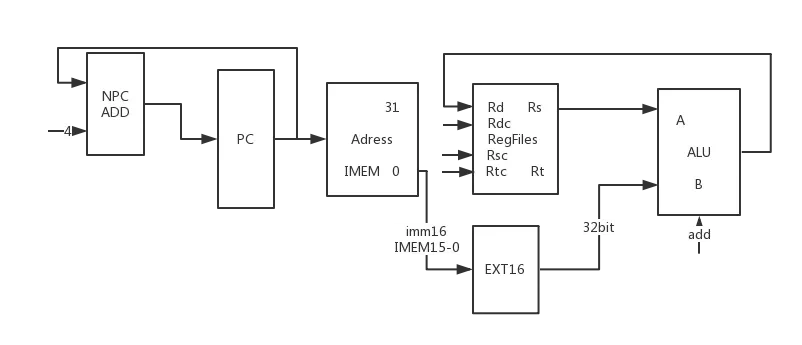

addi

- 格式:addi rt, rs, immediate

- 描述:rt ← rs + immediate; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16

addiu

- 格式:addiu rt, rs, immediate

- 描述:rt ← rs + immediate; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16

andi

- 格式:andi rt, rs, immediate

- 描述:rt ← rs and immediate; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16

ori

- 格式:ori rt, rs, immediate

- 描述:rt ← rs or immediate; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16

xori

- 格式:xori rt, rs, immediate

- 描述:rt ← rs xor immediate; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16

lw

- 格式:lw rt, offset(base)

- 描述:rt ← memoryrs + Sign_ext_offset; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16、DMEM

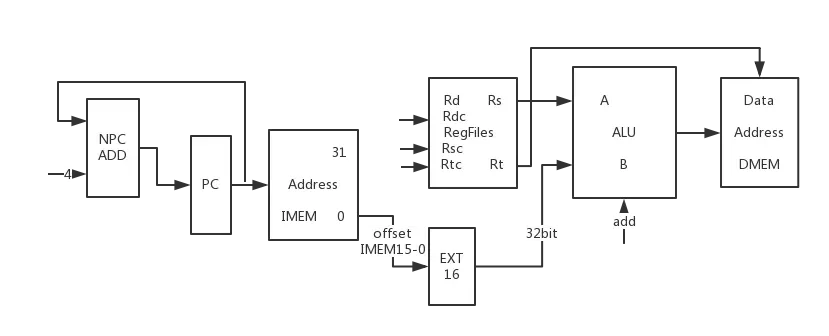

sw

- 格式:sw rt, offset(base)

- 描述:memoryrs + Sign_ext_offset ← rt; PC ← NPC (PC + 4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16、DMEM

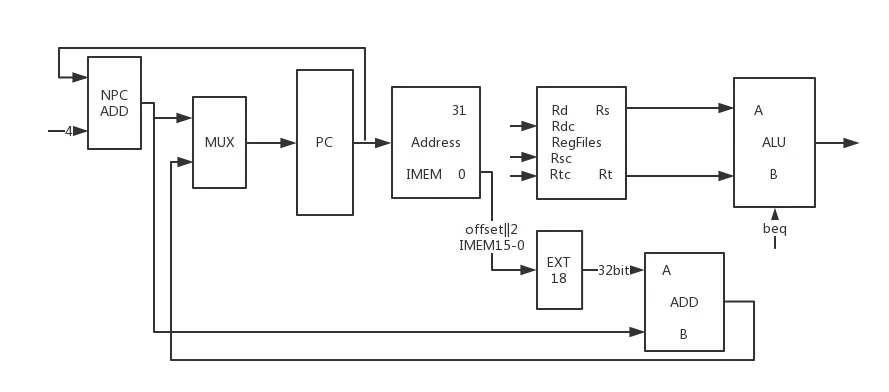

beq

- 格式:beq rs, rt, offset

- 描述:rs == rt, PC ← NPC + Sign_ext (offset||02);否则PC ← NPC(PC+4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT18、ADD

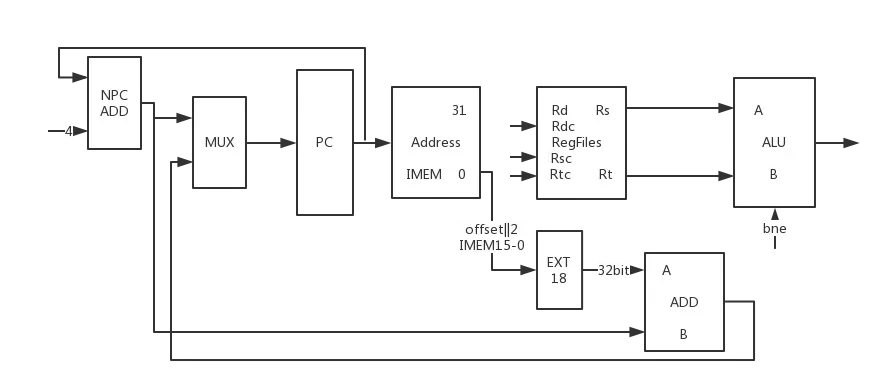

bne

- 格式:bne rs, rt, offset

- 描述:rs != rt, PC ← NPC + Sign_ext (offset||02);否则PC ← NPC(PC+4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT18、ADD

slti

- 格式:slti rt, rs, immediate

- 描述:rt ← (rs < immediate); PC ← NPC(PC+4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16、EXT1

sltiu

- 格式:sltiu rt, rs, immediate

- 描述:rt ← (rs < immediate); PC ← NPC(PC+4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16、EXT1

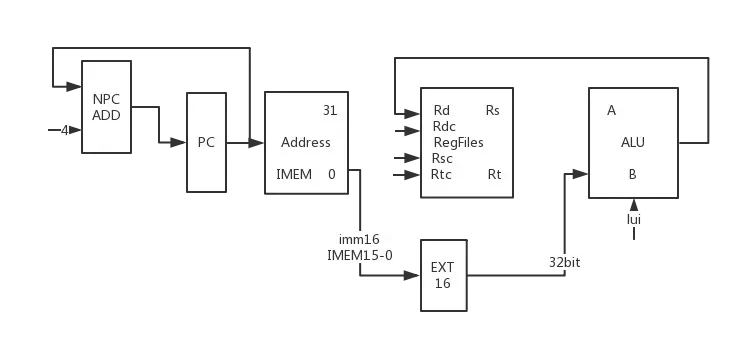

lui

- 格式:lui rt, immediate

- 描述:rt ← immediate || 016; PC ← NPC(PC+4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、EXT16

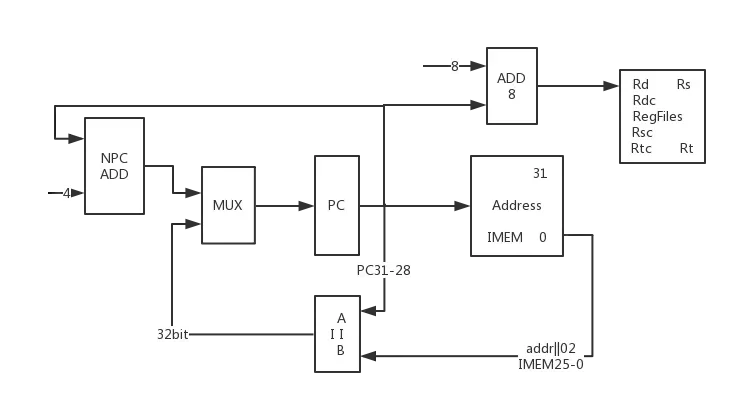

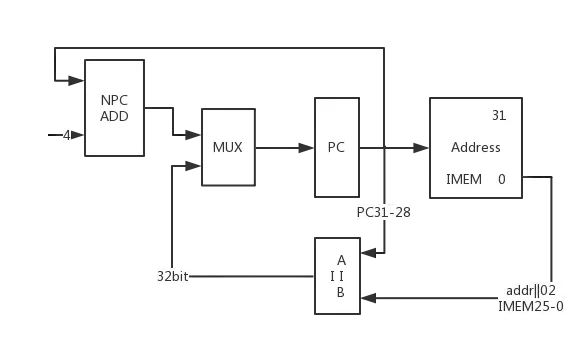

j

- 格式:j target

- 描述:PC ← PC31-28 || instr_index || 02; PC ← NPC(PC+4)

- 部件:PC、NPC、IMEN、ALU、II

jal

- 格式:jal target

- 描述:GPR31 ← PC + 8;PC ← PC31-28 || instr_index || 02;PC ← NPC(PC+4)

- 部件:PC、NPC、IMEN、RegFiles、ALU、II、ADD8