Verilog

31条指令单周期cpu设计(Verilog)-(二)总体设计

详解31条MIPS指令单周期CPU的总体设计方案,包括指令分类、数据通路设计、控制器设计流程,以及lw、sw、jal等难点指令的处理思路。

说在前面

- 开发环境:Vivado

- 语言:Verilog

- cpu框架:Mips

- 控制器:组合逻辑

- 说明:单周期处理器是指所有的指令在一个时钟周期内完成的处理器,尽管不同指令执行时间不同,但对单周期处理器而言,时钟周期必须设计成对所有指令都等长。 在单周期处理器中,一条指令执行过程中数据通路的任何资源都不能被重复使用,因此,任何需要被多次使用的资源(如加法器)都需要设置多个,否则就会发生资源冲突。

总体设计

- 常规套路是从简单的八条指令cpu讲起,然后自己去扩展,31条指令cpu按照八条的那个流程来,无非是工作量大了点,网上八条指令cpu的教程也挺多的。

- 指令介绍

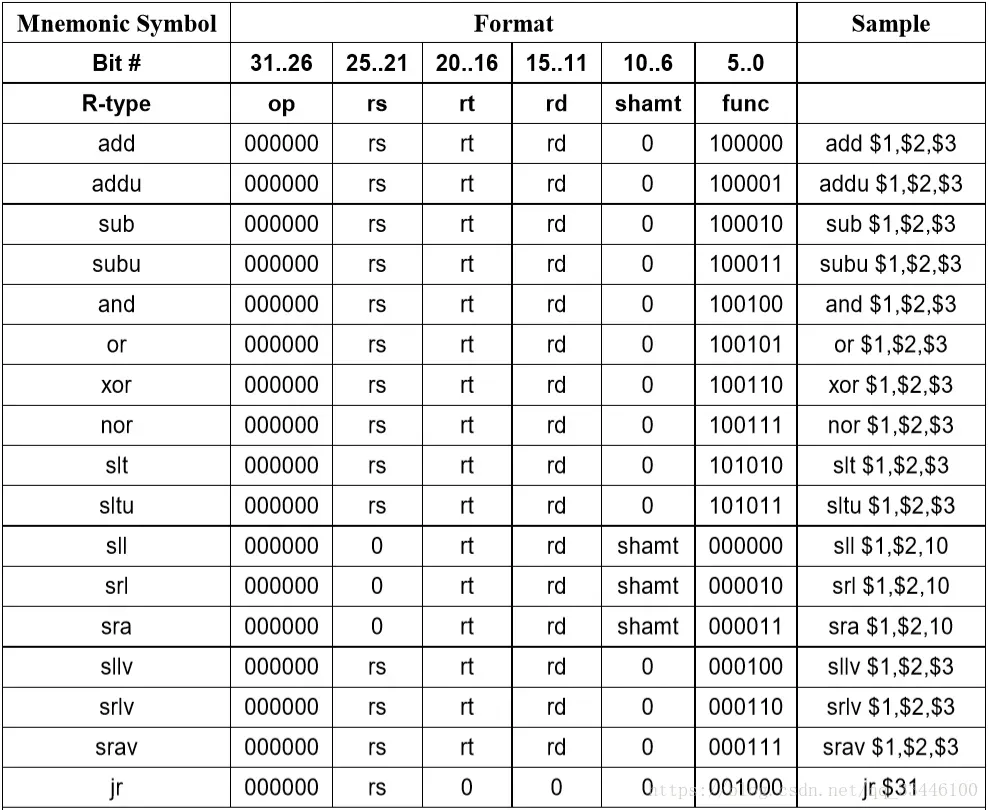

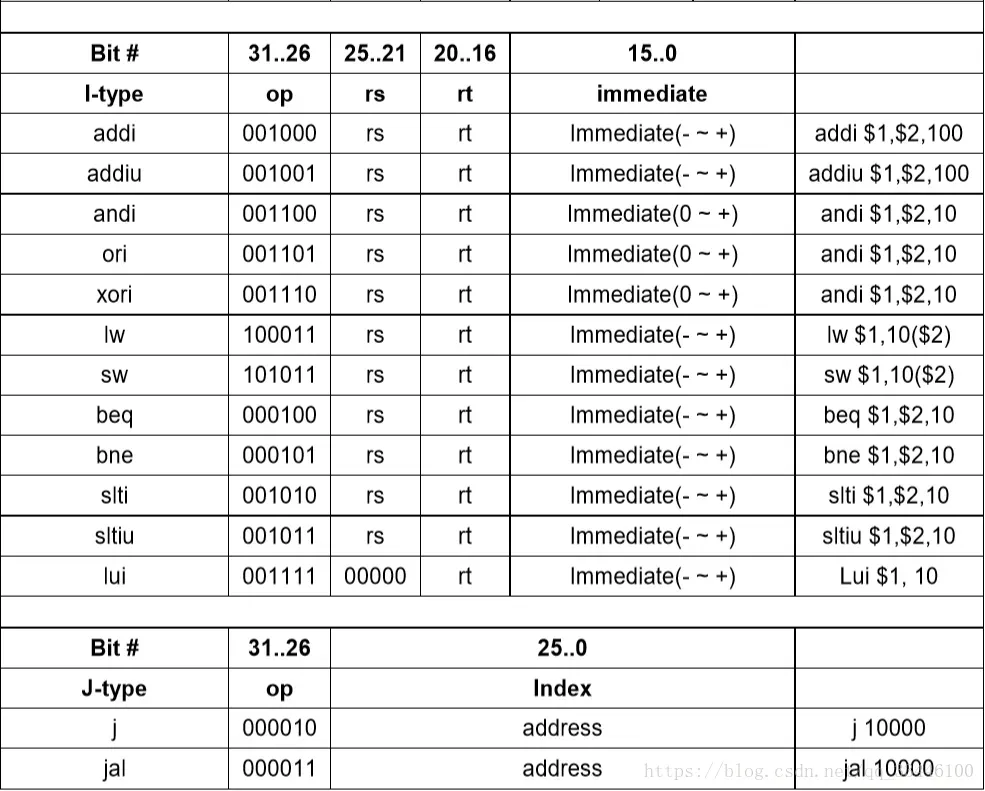

cpu的理论知识就不再多讲了,首先来看看我们要实现的31条指令。

- 这些指令的详细介绍mips官方有给出:

mips指令集

在这部分(这个pdf带跳转功能的)

- 在实现过程中,这31条指令看起来挺多,但是实际上部分指令的数据通路几乎一样,比如add---nor这几个,一定程度上减少了工作量。 注意:这里面比较难的几条指令是lw,sw,jal

设计流程

- 确定各条指令所需要的部件

- 确定各条指令中各个部件的输入输出关系

- 确定数据通路总图

- 根据各条指令所需要的部件以及总通路图,确定指令操作时间表(真值表)

- 根据指令操作时间表,设计控制器

- 根据总通路图以及指令操作时间表,码代码去,编写Verilog代码

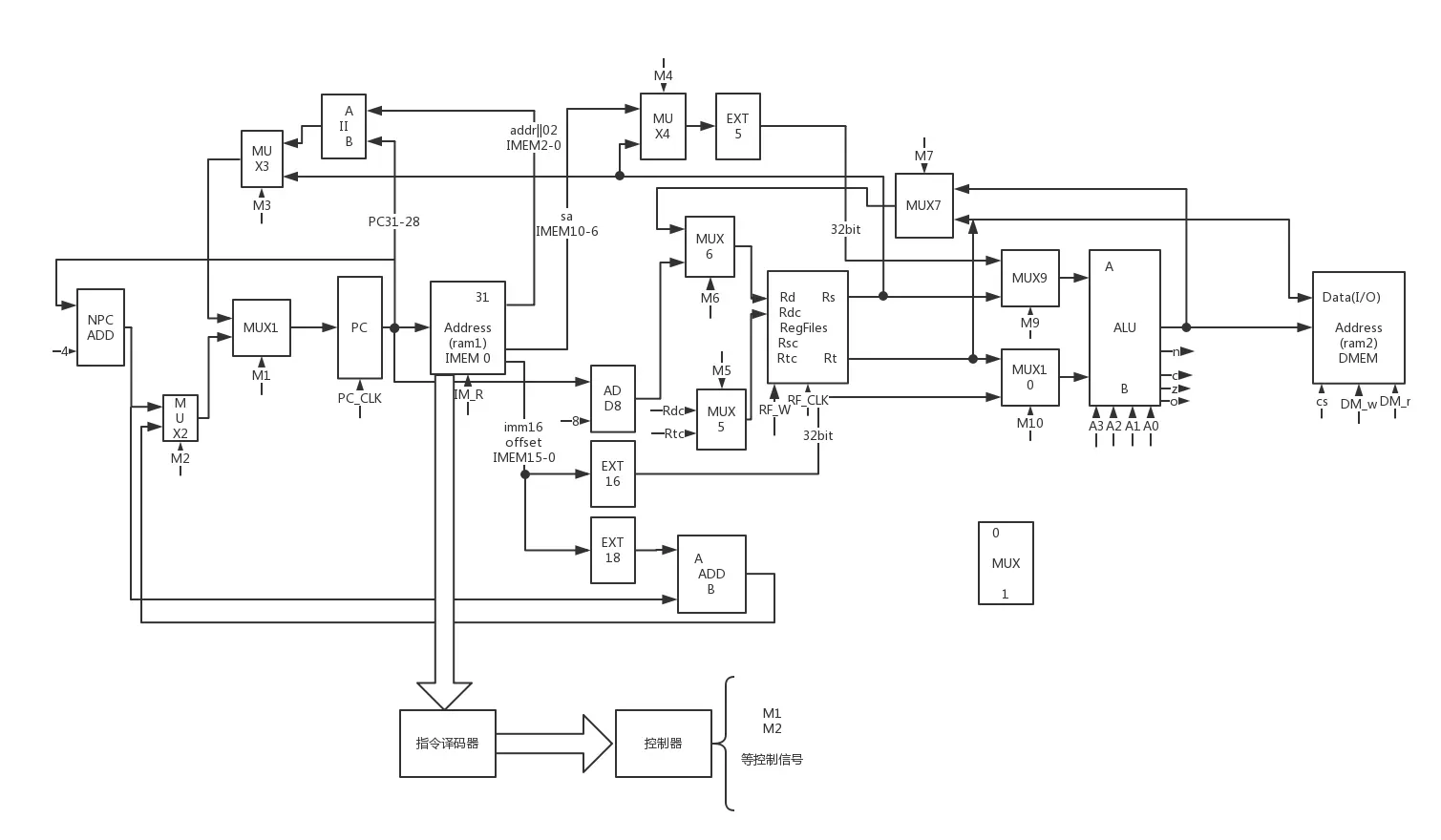

总图

- PC存放指令地址(通过pc+4来读取下一条指令)

- (ram1)IMEM存放指令集

- 根据指令地址从IMEM中取出对应指令

- 指令读取出来后送入指令译码器(具体是哪一条指令)

- 译码后将结果送入控制器,将该条指令相关部件的控制信号置为1(激活),使得cpu中该条指令的数据通路激活,进而执行此指令

- pc+4获取下一条指令,循环操作

以上就是cpu的具体执行过程了,看起来还是挺简单的嘛。

以上就是这节的内容了,下一节将具体介绍各条指令各个部件。