Verilog

31条指令单周期cpu设计(Verilog)-(五)整体数据通路图设计

详解31条MIPS单周期CPU的整体数据通路图设计,包括PC、NPC、ALU、寄存器堆、MUX等部件的连接方式,以及Verilog模块化实现思路。

说在前面

- 开发环境:Vivado

- 语言:Verilog

- cpu框架:Mips

- 控制器:组合逻辑

设计目的

- 我们在用verilog实现这个cpu的时候,一般是先把各个部件单独写一个module,然后再串联起来,这张图就是帮助我们连接各个部件的(通过输入输出关系)。

设计流程

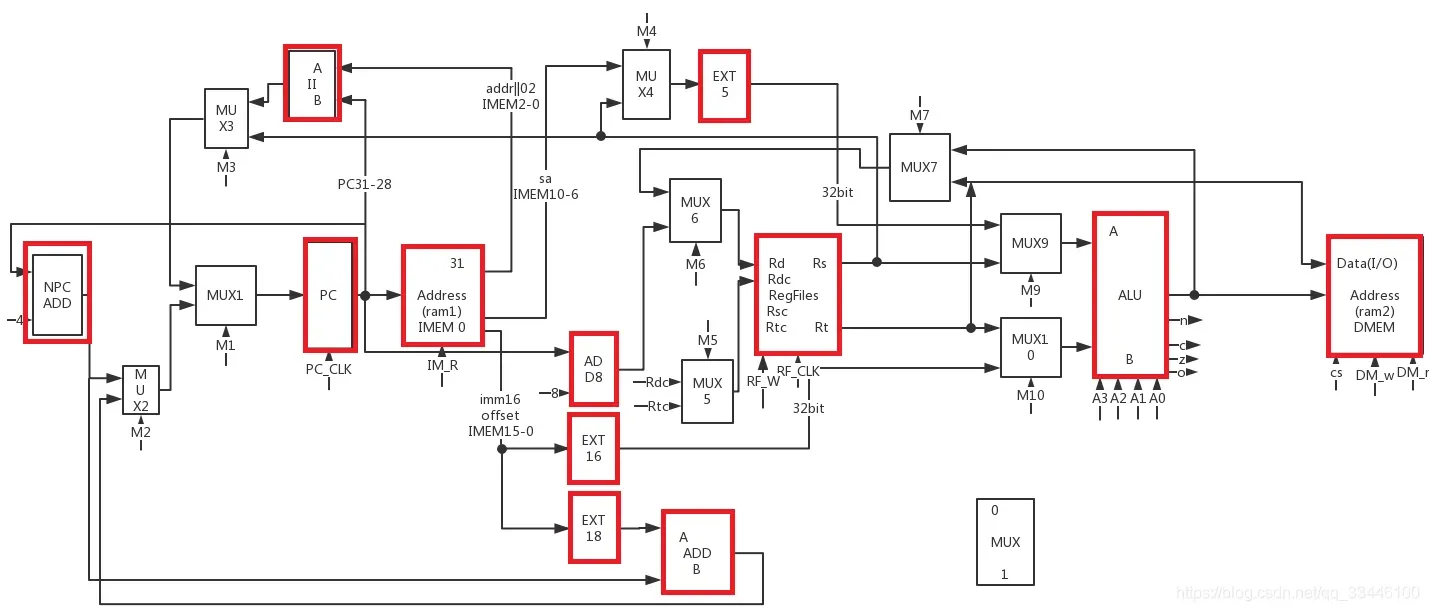

- 把上一章中具体数据通路图 中所有的部件画出来(红色方框部分)

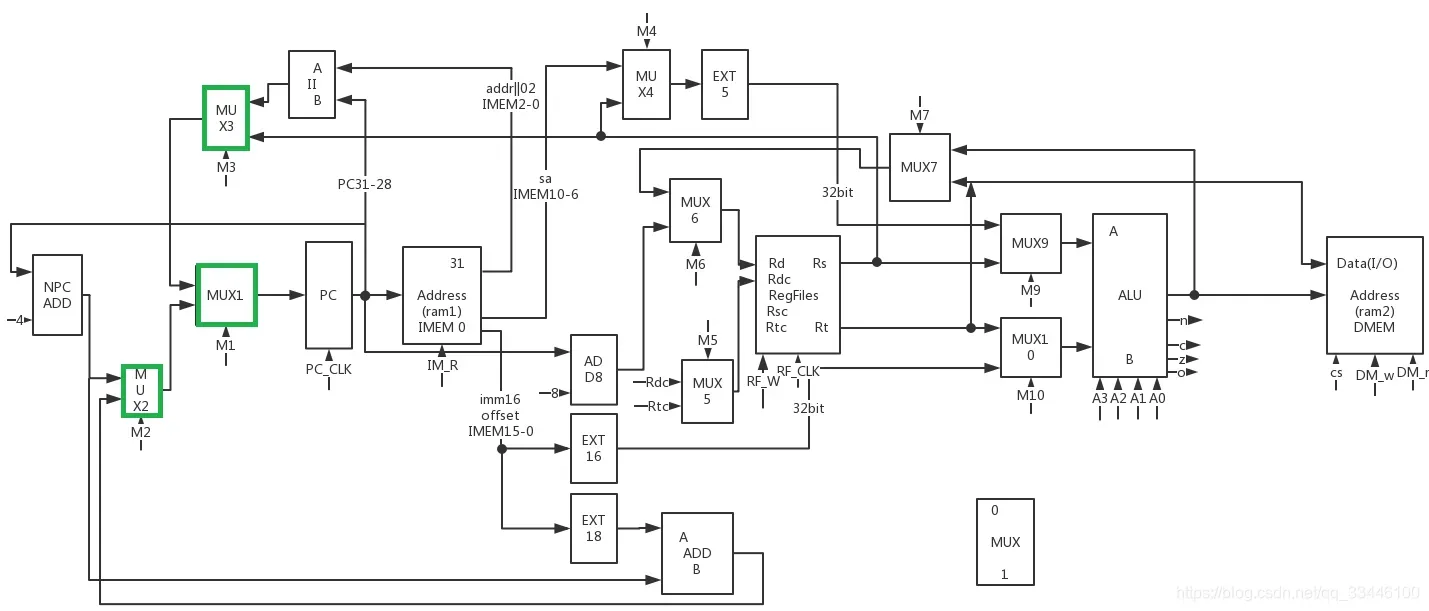

- 根据数据输入输出关系表确定是否需要多路选择器(MUX)、几路选择器

例如,PCPC NPC NPC NPC NPC NPC NPC NPC NPC NPC NPC NPC NPC NPC NPC NPC NPC Rs NPC NPC NPC NPC NPC NPC NPC ADD ADD NPC NPC NPC II II

可以看到其输入有四种,分别是NPC、Rs、ADD、II,可以使用四路MUX或者多个2路MUX,这里采取的是后面一种 。(绿色方框部分)

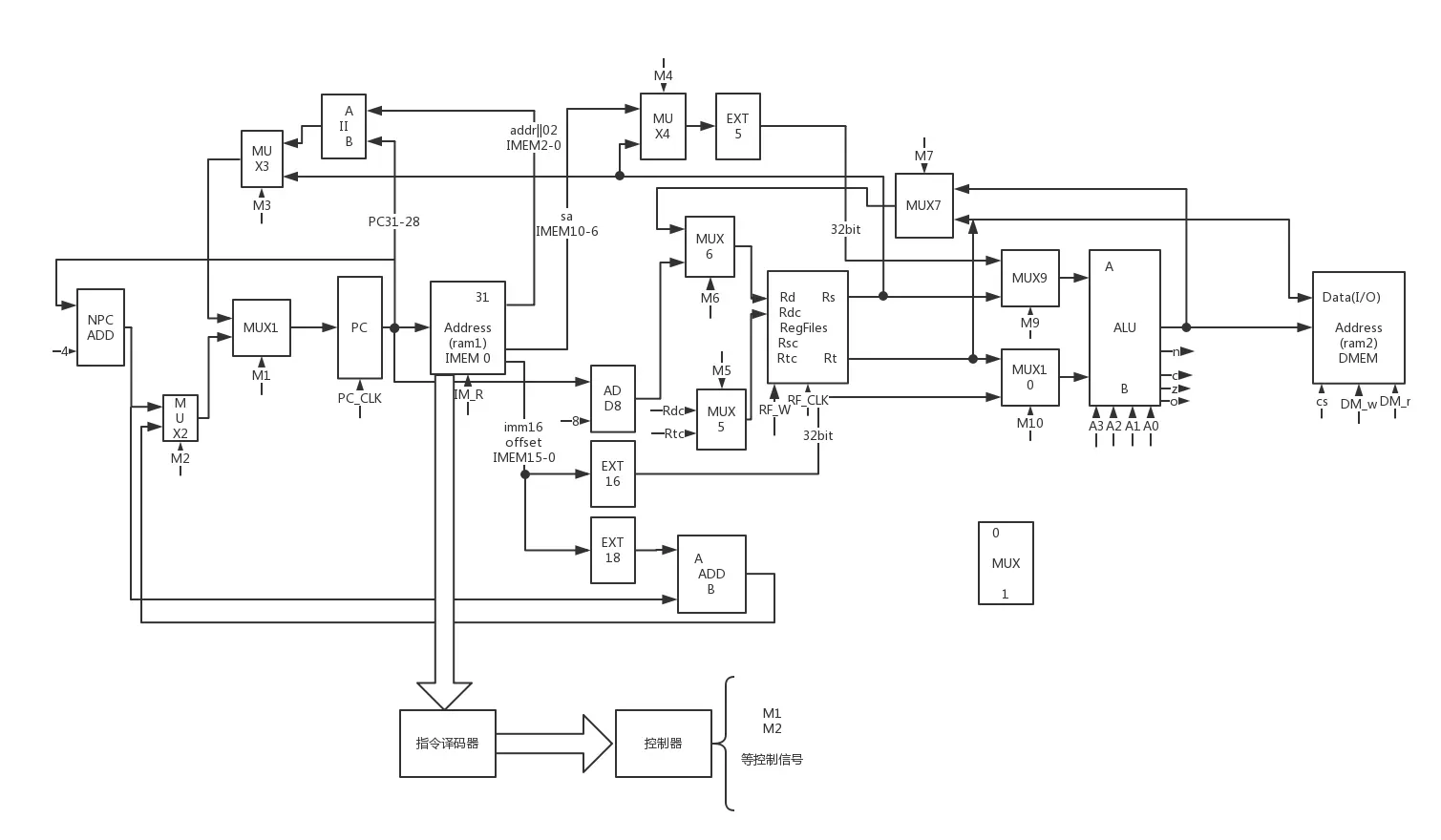

- 最后,根据将所有部件连接

emmmmm,工作量大,但是设计思路应该不是很难